ASPECT MATERIEL DU PIC16F84

![]() DESCRIPTION GENERALE

DESCRIPTION GENERALE

Le PIC16F84

est un microcontrôleur 8 bits de faible coût. Certes, il ne peut se substituer

aux autres microcontrôleurs (68HC11 par exemple) mais il permet toutefois de

créer de nombreuses applications.

De plus,

avec son jeu d'instructions réduit, il est très agréable a utiliser lorsqu'on

désire s'initier à l'étude d'un microcontrôleur.

Enfin, ses

caractéristiques internes et externes sont très appréciable:

![]() > 1K de

mémoire programme

> 1K de

mémoire programme

![]() 68 octets

de RAM

68 octets

de RAM

![]() 64 octets

D'EEPROM

64 octets

D'EEPROM

![]() 13

ENTREE/SORTIE

13

ENTREE/SORTIE

![]() 4 SOURCES

D'INTERRUPTION

4 SOURCES

D'INTERRUPTION

![]() 1

TIMER/COMPTEUR

1

TIMER/COMPTEUR

![]() 1 CHIEN DE

GARDE

1 CHIEN DE

GARDE

![]() MODE SLEEP

(pour une faible consommation)

MODE SLEEP

(pour une faible consommation)

![]() 4 SOURCES

D'OSCILLATEUR SELECTIONNABLE

4 SOURCES

D'OSCILLATEUR SELECTIONNABLE

![]() PROTECTION

DU CODE

PROTECTION

DU CODE

![]() PROGRAMMATION

PAR ISP (In Serial Programming)

PROGRAMMATION

PAR ISP (In Serial Programming)

![]() STRUCTURE EXTERNE

STRUCTURE EXTERNE

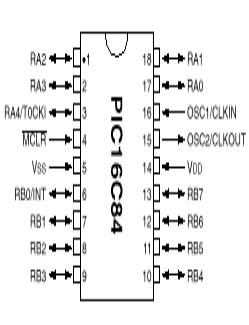

Le PIC16F84

est logé dans un boîtier 18 broches DIL ou SOIC ( version CMS).

La figure

ci-dessous nous décrit le brochage du PIC16F84:

|

PIN 1: 3ème bit du PORTA PIN 2:

4ème bit du PORTA PIN 3:

5ème bit du PORTA / TOCK PIN 4: RESET PIN 5: GND PIN 6: 1er

bit du PORTB PIN 7:

2ème bit du PORTB PIN 8:

3ème bit du PORTB PIN 9:

4ème bit du PORTB |

|

PIN 18:

2ème bit du PORTA PIN 17:

1er bit du PORTA PIN 16:

OSCILLATEUR PIN15:

OSCILLATEUR 2 PIN 14:

VCC PIN 13:

8ème bit du PORTB PIN 12:

7ème bit du PORTB PIN 11:

6ème bit du PORTB PIN 10:

5ème bit du PORTB |

Le PIC

existe aussi en deux versions:

PIC16F 84 :

pour une utilisation dans une gamme d'alimentation classique (4.5 à 5.5V).

PIC16LF84:

pour une gamme étendue de l'alimentation (2 à 6V).

![]() STRUCTURE INTERNE

STRUCTURE INTERNE

L'architecture

interne nous présente les principaux organes qui composent le

microcontrôleur.

Le but ici

n'est pas d'expliquer chaque organe (puisqu'un chapitre leur est consacré) mais

permet de visualiser l'ensemble pour mieux comprendre le fonctionnement du

monochip.

Cependant,

même si les opcodes sont codés sur 14 bits, les données et les

résultats sont et seront toujours sur 8 bits.

![]() ORGANISATION DE LA

MEMOIRE

ORGANISATION DE LA

MEMOIRE

La mémoire

du PIC16F84 est divisée en deux parties distinctes:la mémoire programme et la

mémoire de donnée.

Le premier

contient les instructions du programme ainsi que les vecteurs RESET et

INTERRUPTION.

Dans la

mémoire de donnée se trouve tout les registres nécessaires pour la

configuration et l'utilisation des périphériques internes ainsi que 68 octets

de RAM utilisateurs.

LA

MEMOIRE PROGRAMME

Cette

mémoire de 1K stock le programme. l'emplacement de celui-ci peut être à

n'importe quel endroit de la mémoire. Cependant, il faut savoir que le PIC16F84

,suite à un RESET ou lorsqu'on l'alimente, commence toujours à l'adresse 0000H

(Vecteur RESET).

De plus,

lorsqu'il y a une interruption, et si celle-ci est validée,le microcontrôleur

va à l'adresse 0004H (Vecteur d'INTERRUPTION).

Par

conséquent, garder toujours à l'esprit ces deux adresses particulières de la

mémoire programme.

Voici un

exemple typique d'un programme où l'on utilise l'instruction GOTO et CALL pour

gérer les vecteurs:

ORG 0000

;Début de la

mémoire programme

GOTO

debut ;Là, on indique au microcontrôleur que le début du

programme se trouve à l'adresse debut

ORG

0004 ;Début de

l'adresse d'une l'interruption.

CALL

GESTIN ; S'il y a une interruption, le monochip ira appelle

le sous-programme GESTIN.

debut

bla bla ; début du

programme.

bla bla

LA

MEMOIRE RAM

La mémoire

de donnée est divisée en deux parties. Une partie appelée SFR est encore

divisée en deux pages (Bank0 et Bank 1). Toutes les données de la mémoire sont

appelées registres y compris les données utilisateurs.

LE SFR

(Special Function Registers).

Le SFR

permet de configurer tout les modules internes du PIC16F84 (les PORTS, le TIMER,

la gestion des interruptions, etc...). Il est de plus utilisé par le CPU.

Pour accéder

a l'un de ces registres, il faut d'abord se positionner sur la page (Bank)

appropriée. Ensuite, il suffit de lire ou d'écrire dans le registre nommé.

L'adressage directe

des pages se fait par deux bits du registre de STATUS (RP0 et RP1). On peut

utiliser l'adressage indirecte avec le registre FSR.

La figure

ci-dessous nous montre les différents registres du SFR ainsi que leur adresse

associée.

LE GPR (

General Purpose Register)

Le GPR est

en fait la RAM (8bits) utilisateurs. C'est ici que l'on stocke les variables et

les données. L'utilisation des pages (Bank ) n'est pas nécessaire puisque le

Bank 1 est "mapped" avec le Bank0. Cela signifie qu' écrire une

donnée à l'adresse 0CH ou à l'adresse 8CH revient au même.

Enfin,

l'adressage peut se faire de manière directe ou indirecte (en utilisant le

registre FSR).

LES REGISTRES

![]() PREREQUIS

PREREQUIS

Ces

registres spéciaux font partie du SFR (Special Function Registers) et

configurent le microcontroler: Certains registres initialisent les

périphériques alors que d'autres sont utilisés par le CPU.

Cette partie

décrit uniquement les bits du registre nommé. On donne ici, l'organisation de

la mémoire du PIC16F84:

![]() LES DIFFERENTS REGISTRES

DU PIC16F84

LES DIFFERENTS REGISTRES

DU PIC16F84

LE REGISTRE

INDF (ADRESSE 00, 80H).

Voir le

registre FSR.

LE

REGISTRE FSR (ADRESSE 04,84H).

Le registre

INDF ainsi que FSR permettent l'adressage INDIRECTE.

Le principe

est d'utiliser deux registres intermédiaires pour accéder aux données:

Dans le

premier ,appelé FSR, on inscrit l'adresse (en fait, il est utilisé comme un

pointeur).

L'autre

registre (INDF), contient la valeur qui se trouve à l'adresse définie dans le

FSR.

exemple:

Admettons la

situation suivante:

ADRESSE

VALEUR

10

3

11

4

12

5

Si l'on veut

lire successivement les données se trouvant entre l'adresse 10 et 12, une des

premier méthode est de lire une après une les données.

L'autre

méthode, beaucoup plus souple, réalise la même fonction avec l'adressage

indirecte:

BOU

MOVLW

0X10

MOVWF FSR ; on

initialise le registre FSR avec l'adresse 10

MOVF INDF,W ; on retrouve dans W la

valeur 3

MOVF

VAR ;que l'on met dans VAR

INCF FSR

; on incrémente FSR et a pour

adresse maintenant la valeur 11

GOTO BOU

; et on retourne en BOU. Au prochain passage, VAR conteindra la valeur 4.

LE

REGISTRE TMRO (ADRESSE 01H).

Ce registre

de 8 bits s'incrémente de "1" a chaque impulsion de l'horloge

(externe ou interne). Il est associé au module TIMER/COMPTEUR.

LE

REGISTRE OPTION (ADRESSE 81H)

Le registre

d'OPTION contiens les bits de contrôles du PRESCALER, de l'interruption externe

INT, de la sélection TIMER/COMPTEUR et du "tirage au plus" du PORT B.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

RBPU |

INTEDG |

TOCS |

TOSE |

PSA |

PS2 |

PS1 |

PS0 |

DESCRIPTION

DES BITS

BIT 0,1 et 2:

Sélectionnent le ratio du PRESCALER.

Ces trois

bits déterminent le ratio (effectue une division de la fréquence d'horloge) du

PRESCALER.

TABLEAU:

|

PS2 |

PS1 |

PS0 |

RATIO TMRO |

RATIO WDT |

|

0 |

0 |

0 |

1:2 |

1:1 |

|

0 |

0 |

1 |

1:4 |

1:2 |

|

0 |

1 |

0 |

1:8 |

1:4 |

|

0 |

1 |

1 |

1:16 |

1:8 |

|

1 |

0 |

0 |

1:32 |

1:16 |

|

1 |

0 |

1 |

1:64 |

1:32 |

|

1 |

1 |

0 |

1:128 |

1:64 |

|

1 |

1 |

1 |

1:256 |

1:128 |

BIT 3: PSA (

PreScaler Assignment).

Si PSA=1

alors le prescaler est associé avec le WDT.

Si PSA=0

alors le prescaler est associé avec le TIMER.

BIT 4: TOSE ( TMRO Source Edge).

Ce bit

détermine sur quel front ( montant ou descendant) l'entrée RA4 incrémentera le

registre TMRO

TOSE=1 Front

descendant.

TOSE=0 Front

montant.

BIT 5: TOCS ( TMRO Clock Source)

Il permet de

sélectionner le mode de fonctionnement du TIMER/COMPTEUR.

TOCS=1

sélection de l'horloge externe ( broche RA4) qui correspond au COMPTEUR.

TOCS=0

sélection de l'horloge interne et permet au module de travailler en mode TIMER.

BIT 6: INTEDG ( INTerrupt EDGe)

Si INTEDG=1

alors la broche RBO/INT génère une interruption sur un front montant.

Si INTEDG=0

alors la broche RBO/INT génère une interruption sur un front descendant.

BIT 7: RBPU ( PORT B Pull-Up).

RBPU=1 Le

"tirage au plus" interne du PORT B est desactivé.

RBPU=0 Le

"tirage au plus" interne du PORT B est activé.

LE

REGISTRE STATUS (ADRESSE 03 ET 83H)

Divisé en

plusieurs blocks, il contient:

Le résultat

d'un calcul de l'ALU représenté par les bits C, DC, et Z.

Le status d'un

RESET par l'intermédiaire des bits PD et TO.

L'accès aux

différents bancs de la mémoire par les bits IRP, RP1 et RP0

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

R/W |

R/W |

R |

R |

R/W |

R/W |

R/W |

R/W |

|

IRP |

RP1 |

RP0 |

TO |

PD |

Z |

DC |

C |

DESCRIPTION

DES BITS

BIT0: C (Carry).

Il passe à

"1" lorsque le résultat d'une opération dépasse la valeur FF ou d'un

résultat négatif.

BIT1: DC (Digital Carry).

il se

positionne à "1" lorsque une retenue s'est produite entre les bit 3

et 4.

BIT2: Z (Zero).

quand il est

à "1", il indique que le résultat de l'opération est nul.

BIT3: PD (Power-Down).

PD=1 après

un Power-up ou suite à l'instruction CLRWDT.

PD=0 lorsque

l'instruction SLEEP est exécutée.

BIT4: TO (Time-Out).

il passe à

"1" après les instructions SLEEP et CLRWDT. Lorsque le WDT (chien de

garde) déborde, ce bit passe à "0".

BIT5 et 6:

RP0 et RP1 (bits de sélection de bancs).

Avec ces 2

bits, on accède aux différents bancs de la mémoire.

|

RP1 |

RP0 |

BANC |

ADRESSE |

|

0 |

0 |

0 |

00 à 7F |

|

0 |

1 |

1 |

80 à FF |

|

1 |

0 |

2 |

100 à 17F |

|

1 |

1 |

3 |

180 à 1FF |

BIT7: IRP.

Ce bit n'est

pas utilisé avec le PIC16F84 et doit rester à "0".

LE

REGISTRE TRISA (ADRESSE 85H).

Le registre

TRISA configure chaque E/S du PORTA en ENTREE ou en SORTIE. Apres un RESET,

toutes les E/S sont en ENTREE. Si le bit associé à la porte est à

"1", alors elle sera configurée en ENTREE. Si le bit est à

"0", elle sera en SORTIE.

La broche

RA4 est multipléxée avec l'entrée d'horloge du registre TMRO.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

|

|

|

R/W |

R/W |

R/W |

R/W |

R/W |

|

|

|

|

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

LE

REGISTRE PORTA (ADRESSE 05H).

Le PORTA est

un port de 5 bits (RA0 à RA4). chaque E/S est compatible TTL. La configuration

de chaque BIT du port est déterminée avec le registre TRISA.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

|

|

|

R/W |

R/W |

R/W |

R/W |

R/W |

|

|

|

|

RA4/TOCK |

RA3 |

RA2 |

RA1 |

RA0 |

LE

REGISTRE TRISB (ADRESSE 86H)

Le registre

TRISB configure chaque E/S du PORTB en ENTREE ou en SORTIE. Apres un RESET,

toutes les E/S sont en ENTREE. Si le bit associé à la porte est à

"1", alors elle sera configurée en ENTREE. Si le bit est à

"0", elle sera en SORTIE.

La broche

RB0 est multiplexée avec l'interruption INT.

les broches

RB4 à RB4, à condition qu'elles sont configurées en ENTREE, peuvent générer une

interruption lorsqu'elles changent d'états.

Enfin,

toutes les broches du PORTB bénéficient d'un "tirage au plus"

interne.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

LE

REGISTRE PORTB (ADRESSE 06H).

Le PORTB est

un port bi-directionnel de 8 bits. Toutes les broches sont compatibles TTL. La

configuration du PORTB est réalisée avec le registre TRISB.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0 |

LE

REGISTRE EEDATA (ADRESSE 08H).

Ce registre

de 8 bits permet de lire ou d'écrire une donnée dans la mémoire non volatile

(EEPROM).

LE

REGISTRE EEADR (ADRESSE 09H).

Registre de

8 bits qui contient l'adresse de la donnée se trouvant dans l'EEPROM.

LE

REGISTRE EECON1 (ADRESSE 88H)

C'est un

registre de contrôle qui permet d'exécuter une lecture ou une écriture dans

l'EEPROM.

Seuls les 5

bits de poids faible sont utilisés.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

|

|

|

R/W |

R/W |

R/W |

W |

W |

|

|

|

|

EEIF |

WRERR |

WREN |

WR |

RD |

DESCRIPTION

DES BITS

BIT 0: RD

(ReaD EEPROM).

Lorsque ce

bit est mis à "1", il indique au microcontroler que l'on souhaite une

lecture de l'EEPROM.

Apres le

cycle de lecture, il est mis automatiquement à 0.

BIT 1: WR (WRite EEPROM).

Lorsque ce

bit est mis à "1", il indique au microcontroler que l'on souhaite une

écriture de l'EEPROM.

Apres le

cycle d'écriture, il est mis automatiquement à 0.

BIT 2: WREN (EEPROM WRite ENABLE).

C'est un bit

de confirmation d'écriture dans l'EEPROM. En effet, il ne suffit pas de définir

un cycle d'écriture uniquement avec le bit WR. Il faut impérativement valider

le bit WREN (WREN=1) pour autoriser une écriture.

BIT 3: WRERR (EEPROM WRite ERROR flag).

Ce drapeau

indique qu'une erreur c'est produite lors d'un cycle d'écriture dans l'EEPROM.

WRERR=1 une

opération d'écriture a échoué.

WRERR=0 le

cycle d'écriture c'est déroulé normalement.

BIT 4: EEIF ( EEPROM Interrupt

Flag).

EEIF est une

drapeau qui génère une interruption lorsqu'un cycle d'écriture c'est déroulé

normalement. Il doit être mis à 0 lors de la routine d'interruption.

EEIF=1

l'opération c'est déroulé correctement.

EEIF=0 soit

l'opération n'a pas commencé, soit n'est pas terminée.

LE

REGISTRE EECON2 (ADRESSE 89H).

Ce registre

de 8 bits est exclusivement utilisé pour les séquences d'écritures dans

l'EEPROM. Il n'a pas d'adresse physique et la lecture de ce registre retourne

une valeur nulle.

LE

REGISTRE INTCON (ADRESSE 0B et 8BH)

Le registre

INTCON contient tout les bits de validation de chaque source d'interruption

ainsi que leur drapeau (Flag).

Les drapeaux

doivent être mise à 0 après l'interruption.

TABLEAU

|

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

GIE |

EEIE |

TOIE |

INTE |

RBIE |

TOIF |

INTF |

RBIF |

DESCRIPTION

DES BITS

BIT 0: RBIF (

RB port change Interrupt Flag).

C'est un

drapeau d'interruption qui indique un changement d'état du PORT B (RB4 à RB7).

RBIF=1 une

broche (RB4 à RB7) à changé d'état.

RBIF=0 pas

de changement d'état.

BIT 1: INTF

(INT interrupt Flag).

Drapeau

d'interruption de l'entrée RB0.

RBIF=1 une

interruption est apparue.

RBIF=0 pas

d'interruption.

BIT 2: TOIF ( TMRO Overflow Interrupt Flag).

Ce drapeau

indique un dépassement du registre TMRO (passage de FF à 00).

TOIF=1

dépassement de TMRO.

TOIF=0 pas

de dépassement.

BIT 3: RBIE

(RB Interrupt Enable).

Bit de

validation qui autorise une interruption lors d'un changement d'état du PORT B

(RB4 à RB7).

RBIE=1

Autorise l'interruption.

RBIE=0 Les

changement d'état du PORT B (RB4 à RB7) ne généront pas d'interruption.

BIT 4: INTE (

INT interrupt Enable).

Valide ou

non l'interruption généré par la broche RB0/INT

INTE=1

Valide l'interruption INT.

INTE=0 Pas

d'interruption provenant de INT.

BIT 5: TOIE (TMRO Overflow Interrupt Enable).

Autorise ou

non l'interruption provoqué par le dépassement du registre TMRO (passage de FF

à 00)

TOIE=1

Valide l'interruption.

TOIE=0 Pas

d'interruption provenant du registre TMRO.

BIT 6 : EEIE (EE write Interrupt Enable).

Ce bit

autorise ou non une interruption lorsqu'un cycle d'écriture dans L'EEPROM c'est

déroulé normalement.

EEIE=1

Génère une interruption lorsqu'une cycle d'écriture c'est déroulé normalement.

EEIE=0 Pas

d'interruption.

BIT 7: GIE

(Global Interrupt Enable).

Ce bit

autorise ou non toutes les interruptions.

GIE=1 Toutes

les interruptions sont prises en compte par le microcontroler.

GIE=0 Aucune

interruption ne sera validée.

LE

REGISTRE PCL (ADRESSE 02, 82H).

Le PC

(Program Counter) est un pointeur de 13 bits qui contient l'adresse de la

prochaine instruction a exécuter.

Il est

composé de deux registres:

le PCL:

C'est un registre de 8 bits accessible en écriture et en lecture et compose la

partie basse du PC.

Le PCLATH:

C'est un registre de 8 bits dont seuls les 5 bits de poids faible sont

utilisés. Non accessible directement, il définie la partie haute du PC. Il

permet d'une part, de sélectionner les différentes page de la mémoire programme

et d'autre part, son contenue est transféré lorsque le PC est chargé avec une

nouvelle valeur.

REMARQUE:

Le PIC16F84 n'a que 1 K de programme mémoire. Par conséquent, les bits 3 et 4

du PCLATH ne sont pas utilisés.

LE REGISTRE

PCLATH (ADRESSE 0A, 8AH).

Voir le

registre PCL.

LA PERIPHERIE

![]() LE PORTA ET B

LE PORTA ET B

les PORTS A

et B sont des ENTREE/SORTIE réalisant le dialogue entre le microcontroler et

son environnement extérieur. Le PI16F84 possède 13 entrées/sorties reparties

sur deux PORTS (A et B) de la manière suivante :

![]() Le PORT

A est un bus de donnée bidirectionnel de 5 bits. Chaque bit peut être

configuré en ENTREE ou en SORTIE. Le niveau d’ENTREE/SORTIE est compatible TTL.

Le PORT

A est un bus de donnée bidirectionnel de 5 bits. Chaque bit peut être

configuré en ENTREE ou en SORTIE. Le niveau d’ENTREE/SORTIE est compatible TTL.

![]() Le PORT B

est aussi un bus de donnée bidirectionnel, mais de 8 bits. Chaque bit peut être

configuré en ENTREE ou en SORTIE. Le niveau d’ENTREE/SORTIE est compatible TTL.

Le PORT B

est aussi un bus de donnée bidirectionnel, mais de 8 bits. Chaque bit peut être

configuré en ENTREE ou en SORTIE. Le niveau d’ENTREE/SORTIE est compatible TTL.

STRUCTURE

INTERNE DU PORT A

Le PORT A

est constitué de 5 bits. Les bits RA0 à RA3 ont un niveau d'entrée TTL et une

paire de transistors CMOS complémentaires en sortie.

Le bit RA4

est lui aussi compatible TTL en entrée mais sa sortie est en DRAIN OUVERT.

De plus,

configuré en ENTREE, il peut être utilisé pour l'incrémentation du compteur

interne TMRO.

C'est le

registre de direction TRISA qui détermine l'orientation de chaque broche du

port. Un "1" dans le registre TRISA positionne la broche associée en

ENTREE, alors qu'un "0" la met en SORTIE.

Après un

RESET, le PORTA est configuré en ENTREE.

![]() Une lecture du PORTA lit

la valeur qui se trouve directement sur les broches, alors qu'une écriture

s'effectue en revanche en plusieurs étapes :

Une lecture du PORTA lit

la valeur qui se trouve directement sur les broches, alors qu'une écriture

s'effectue en revanche en plusieurs étapes :

Lecture du

port - modification de la donnée lue - écriture dans les

bascules de donnée.

REGISTRE ASSOCIES.

|

ADR |

NOM |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

05H |

PORTA |

|

|

|

RA4/TOCK |

RA3 |

RA2 |

RA1 |

RA0 |

|

85H |

TRISA |

|

|

|

TRISA4 |

TRISA3 |

TRISA2 |

TRISA1 |

TRISA0 |

STRUCTURE

INTERNE DU PORT B

C'est un

port bidirectionnel de 8bits (RB0 a RB7).

Chaque

broche est compatible TTL. L'orientation de chaque bit se fera avec le registre

de direction TRISB. On remarquera au passage l'utilisation d'un BUFFER

tri-states (3 états) pour l'étage de SORTIE. Celui-ci passe à l'état de HAUTE

IMPEDANCE lorsqu'une broche est configurée en ENTREE (un "1" dans le

registre TRISB).

Un tirage au

plus, "weak pull-up" (WPU), a été intégré sur chaque broche. Il

permet ainsi d'avoir un "1" logique lorsqu'une broche est en ENTREE

(évitant ainsi des composants externes supplémentaires). Le contrôle s'effectue

avec le bit RBPU du registre d'OPTION (actif à l'état bas). Si une broche

est configurée en SORTIE ou lors d'un POWER-ON-RESET (POR), l'étage WPU

sera alors automatiquement inhibé. Les 4 broches (RB4 à RB7) peuvent générer

une INTERRUPTION (uniquement si elles sont configurées en ENTREE). En regardant

la structure interne, on constate que les 2 verrous et la porte logique OU

EXCLUSIF forment un ensemble qui compare la dernière valeur lue et la valeur

présente sur la broche. S’il y a une différence (un changement d'état), la

sortie de la porte sera au niveau haut.

Pour effacer

l'interruption, on devra alors, dans la routine d'interruption, lire (écrire)

le port ou mettre à zéro le drapeau RBIF du registre INTCON. Cette interruption

peut être utilisée pour "réveiller" le PIC lorsqu'il est en mode

SLEEP.

La broche

RB0 peut elle aussi générer une INTERRUPTION (drapeau INTF du registre INTCON).

![]() Comme pour le PORTA, une

lecture du port lit la valeur actuelle sur les broches. Tout au contraire, une

écriture passe par 3 étapes distinctes : lecture du port, modification de la

valeur lue, réécriture dans les verrous de donnée.

Comme pour le PORTA, une

lecture du port lit la valeur actuelle sur les broches. Tout au contraire, une

écriture passe par 3 étapes distinctes : lecture du port, modification de la

valeur lue, réécriture dans les verrous de donnée.

![]() Cela peut poser problème

lorsqu'une broche est utilisée en ENTREE puis en SORTIE. On ne peut en effet

connaître son état dans la mesure où est inconnue la valeur qu'elle avait en

ENTREE.

Cela peut poser problème

lorsqu'une broche est utilisée en ENTREE puis en SORTIE. On ne peut en effet

connaître son état dans la mesure où est inconnue la valeur qu'elle avait en

ENTREE.

REGISTRE ASSOCIES.

|

ADR |

NOM |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

06H |

PORTB |

RB7 |

RB6 |

RB5 |

RB4 |

RB3 |

RB2 |

RB1 |

RB0/INT |

|

86H |

TRISB |

TRISB7 |

TRISB6 |

TRISB5 |

TRISB4 |

TRISB3 |

TRISB2 |

TRISB1 |

TRISB0 |

|

81H |

OPTION |

RBPU |

|

|

|

|

|

|

|

![]() LE TIMER

LE TIMER

Le

TIMER/COMPTEUR est une interface programmable, qui permet de réaliser une

large gamme d’applications : compteur d’impulsion, fréquencemètre,

générateur de fonction, etc… Bref, il convient pour tous les montages

nécessitant une base de temps de précision.

La

différence entre un TEMPORISATEUR (TIMER) et un COMPTEUR (COUNTER) réside dans

le choix de l’horloge qui l’incrémente. Si l’on opte pour une horloge externe,

on disposera alors d’un COMPTEUR. Dans ce cas, l’horloge sera synchronisée avec

l’horloge interne du microcontroler.

Si le choix

se porte sur l’horloge interne, l’interface se comportera comme un TIMER.

Le principe

est assez simple : il s’agit en effet d’incrémenter le registre TRMO de 1à

chaque impulsion d'horloge interne ou externe. Il est possible d’intercaler un

autre compteur (PRESCALER) afin de réaliser une division supplémentaire de la

fréquence de l’horloge.

La structure

interne nous présente les principaux organes qui composent un TIMER. A part le

registre TMR0, chacun d'eux est configuré avec un ou plusieurs BITS du registre

d'OPTION.

LE REGISTRE

TMR0

C'est un

registre 8 bits accessible en lecture ou en écriture. Il est incrémenté à

chaque cycle d'horloge de PSOUT.

Dans le cas

d'un dépassement (lorsque la valeur passe de FF à 00), le drapeau TOIF passe a

"1" et génère une interruption (s'il a été validé dans le registre

INTCON).

![]() Il faut impérativement

remettre à "0" le bit TOIF après avoir traité l'interruption.

Il faut impérativement

remettre à "0" le bit TOIF après avoir traité l'interruption.

LE

DIVISEUR PROGRAMMABLE OU PRESCALER

C'est en

fait un compteur de 8 bits qui divise la fréquence PSIN par le ratio défini

avec les bits TS0, TS1, TS2 (voir le tableau récapitulatif pour les ratios).

![]() Le prescaler est partagé

avec le WDT (WatchDog Timer). Par conséquent, il n'est pas possible d'utiliser

le diviseur simultanément avec le WDT et le TIMER/COMPTEUR. Si le PRESCALER est

indispensable aux deux, l'alternative est alors la seule solution.

Le prescaler est partagé

avec le WDT (WatchDog Timer). Par conséquent, il n'est pas possible d'utiliser

le diviseur simultanément avec le WDT et le TIMER/COMPTEUR. Si le PRESCALER est

indispensable aux deux, l'alternative est alors la seule solution.

C'est le bit

PSA qui détermine l'appartenance du prescaler. Avec un niveau bas

("0") sur PSA, le diviseur est associé au TIMER/COMPTEUR. Si PSA est

à "1", il appartient alors au WDT.

![]() Toute écriture dans le

block du TIMER/COMPTEUR efface le contenu du prescaler.

Toute écriture dans le

block du TIMER/COMPTEUR efface le contenu du prescaler.

SELECTION

DE L'HORLOGE

Le choix de

l'horloge interne ou externe définit le mode TIMER ou COMPTEUR. La mise à zéro

du bit TOCS sélectionne le TIMER et inhibe l'horloge externe.

Si TOCS est

à "1", le mode COMPTEUR est pris en compte. Dans ce cas de figure, un

autre bit, TOSE, définit le front sur lequel aura lieu l'acquisition ( TOSE=0

pour un front montant, TOSE=1 pour un front descendant).

![]() Dans le cas du COMPTEUR,

l'horloge externe est synchronisée avec l'horloge interne. Il en résulte deux

conséquences à ne pas négliger:

Dans le cas du COMPTEUR,

l'horloge externe est synchronisée avec l'horloge interne. Il en résulte deux

conséquences à ne pas négliger:

Premièrement,

il y a un retard entre l'acquisition de l'horloge externe et l'incrémentation (

typiquement deux cycles d'horloge interne) du registre TMRO.

Deuxièmement,

pour que l'impulsion soit prise en compte, il faut absolument que la période de

l'horloge externe soit au minimum égale à 4 cycles d'horloge interne (sans

prescaler),ou à 4 cycles d'horloge interne/ N avec l'utilisation du prescaler (

N étant le ratio).

REGISTRE

ASSOCIES.

On indique

ici que les bits utilisés.

|

ADR |

NOM |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

01H |

TMR0 |

|

|

|

|

|

|

|

|

|

0BH |

INTCON |

GIE |

|

TOIE |

|

|

TOIF |

|

|

|

81H |

OPTION |

|

|

TOCS |

TOSE |

PSA |

PS2 |

PS1 |

PS0 |

|

85H |

TRISA |

|

|

|

TRISA4 |

|

|

|

|

![]() LE CHIEN DE GARDE

LE CHIEN DE GARDE

Le chien de

garde, "WATCHDOG TIMER" (WDT), permet d'assurer, de manière simple,

le bon déroulement d'un programme. Si le programme

" plante ", le WDT génère un RESET ou un autre événement

permettant, soit à l'utilisateur, soit au logiciel, de réagir en conséquence.

Le WDT du

PIC16F84 est composé d'un oscillateur interne à réseau RC indépendant et d'un

compteur 8bits. La période de l’oscillateur varie en fonction de la température

et de la tension d'alimentation (de 10ms à 60ms dans les cas extrêmes).

DEROULEMENT

A chaque

cycle d’horloge de l’oscillateur, le compteur s’incrémente de 1. A la fin du

comptage, c’est à dire lorsque le compteur passe de FF à 00, le WDT met le bit

TO (Time Out) du registre STATUS à 0. Si l’on souhaite augmenter le temps du chien

de garde, on peut utiliser le prescaler. C’est un autre compteur binaire

programmable qui est mis en série avec le compteur du WDT et permet ainsi

d’augmenter le temps (jusqu'à 2.3 secondes). Il est important de noter que le

prescaler est partagé avec le TIMER. Il n’est donc pas possible de les utiliser

simultanément.

Le WDT est

configurable uniquement lors de la programmation du microcontroler, c’est à

dire dans le "mot de configuration".

APPLICATION

Le

fonctionnement est assez simple : il suffit d'abord de le valider dans le

"mot de configuration" puis de sélectionner la période du WDT (avec

ou sans prescaler), et enfin d'effacer le registre WDT périodiquement (avec

l'instruction CLRWDT). Si le programme " plante ", il n'y a

plus de remise à 0 et le bit TO s'active. Dans le mode SLEEP, le programme

continue à l'instruction suivante. En revanche, en mode normal, cela génère un

RESET.

![]() Les instructions CLRWDT

et SLEEP effacent les registres WDT et le prescaler.

Les instructions CLRWDT

et SLEEP effacent les registres WDT et le prescaler.

LE

PRESCALER

C’est un

compteur binaire qui permet de diviser la fréquence de l’horloge. Suivant le

ratio défini par l’utilisateur, la division s’étend de 1 à 128.

REGISTRE

ASSOCIES.

On indique

ici que les bits utilisés.

|

ADR |

NOM |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

2007H |

CONFIG |

|

|

|

|

|

WDTE |

|

|

|

81H |

OPTION |

|

|

|

|

PSA |

PS2 |

PS1 |

PS0 |

![]() L’EEPROM

L’EEPROM

C'est une

mémoire qui permet de stocker jusqu'à 64 octets de données de façon non

volatile (les données restent en mémoire même en cas de coupure de

l'alimentation).

Les données

de cette EEPROM ne sont pas directement accessibles. Il faut alors utiliser

l'adressage indirect à travers 4 registres (EECON1, EECON2, EEDATA, EEADR) du registre

SFR (Registre de Fonction Spécial) :

- EEDATA

C'est un

registre de 8 bits utilisé pour lire ou écrire une donnée dans l'EEPROM. La

donnée de la mémoire EEPROM est envoyée dans ce registre et y est maintenue

jusqu'au prochain cycle de lecture ou d'écriture.

- EEADR

C'est un

registre de 8 bits qui définit l'adresse de l'octet à lire ou à écrire.

Logiquement, il peut adresser jusqu'à 256 octets, mais le PIC16F84 n'en possède

que 64. Aussi la valeur de EEADR sera-t-elle comprise entre 00h et 3Fh.

- EECON1

C'est un

registre de 8 bits dont seuls les 5 premiers, de poids faible, sont utilisés

(bit 0 à bit 4).

![]() RD,

"READ", (bit 0) et WR, "WRITE", (bit 1) gèrent

respectivement la lecture et l'écriture de l'EEPROM. La sélection se fait par

la mise à "1" du bit. En fait, seule la mise à "1" est

possible. RD et WR sont automatiquement mis à "0" après la fin de

chaque cycle.

RD,

"READ", (bit 0) et WR, "WRITE", (bit 1) gèrent

respectivement la lecture et l'écriture de l'EEPROM. La sélection se fait par

la mise à "1" du bit. En fait, seule la mise à "1" est

possible. RD et WR sont automatiquement mis à "0" après la fin de

chaque cycle.

![]() Le bit

WREN, "WRITE ENABLE", (bit 2) est un bit supplémentaire pour la

procédure d'écriture. Après la fin du cycle, il faut le mettre à 0.

Le bit

WREN, "WRITE ENABLE", (bit 2) est un bit supplémentaire pour la

procédure d'écriture. Après la fin du cycle, il faut le mettre à 0.

![]() Le bit

WRERR, "WRITE ERROR", (bit3) est un drapeau qui passe à l'état haut

lorsqu'il y a eu un problème d'écriture ( par exemple, à la suite d’un reset ou

d’un time-out du WDT). Dans ce cas, les données dans EEDATA et EEADR sont

conservées et il est donc possible de recommencer le cycle d'écriture sans

recharger les valeurs.

Le bit

WRERR, "WRITE ERROR", (bit3) est un drapeau qui passe à l'état haut

lorsqu'il y a eu un problème d'écriture ( par exemple, à la suite d’un reset ou

d’un time-out du WDT). Dans ce cas, les données dans EEDATA et EEADR sont

conservées et il est donc possible de recommencer le cycle d'écriture sans

recharger les valeurs.

![]() Enfin, le

bit EEIF, "EEprom Interupt Flag", (bit4) est aussi un drapeau qui, à

l'état haut, indique que l'opération d'écriture s'est déroulé normalement. Il

doit être mis à 0 à la fin de la procédure.

Enfin, le

bit EEIF, "EEprom Interupt Flag", (bit4) est aussi un drapeau qui, à

l'état haut, indique que l'opération d'écriture s'est déroulé normalement. Il

doit être mis à 0 à la fin de la procédure.

-EECON2

C'est un

registre de 8 bits particulier qui est réservé uniquement au cycle d'écriture.

REGISTRE

ASSOCIES.

On indique

ici que les bits utilisés.

|

ADR |

NOM |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

08H |

EEDATA |

|

|

|

|

|

|

|

|

|

0BH |

INTCON |

GIE |

|

TOIE |

|

|

TOIF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

81H |

OPTION |

|

|

TOCS |

TOSE |

PSA |

PS2 |

PS1 |

PS0 |

![]() LES INTERRUPTIONS

LES INTERRUPTIONS

Le monochip

traite des informations provenant de son environnement extérieur. Une première

forme de saisie est la scrutation : le microcontroler va scruter son

environnement par l’intermédiaire des PORTS A et B. Ce principe est correct

tant que les informations sont présentes sur les ports. Ce procédé ne convient

plus dès lors qu’un événement externe non prévisible se produit : on

appelle une interruption cette deuxième manière de traiter des informations.

Une

interruption provoque l’arrêt du programme en cours pour permettre le passage

au sous-programme d’interruption. Après la fin de cette routine, le

microcontroler reprend le programme à l’endroit où il s’était arrêté. Comme une

interruption est un événement asynchrone, il faut alors sauvegarder le contexte

dans lequel se trouvait le microcontroler avant l’interruption, afin qu’il

puisse reprendre correctement la continuité du programme.

Le PIC16F84

possède 5 sources d'interruption : 3 externes (RB0, RB4 à RB7 du PORTB et

évidemment le RESET) et 2 internes (fin de cycle d'écriture de l'EEPROM et

dépassement du registre TMR0).

On ne

traitera pas ici du RESET, interruption particulière à laquelle un chapitre

spécifique est consacré.

Chaque

source d'interruption est constituée d'un drapeau et d'un bit de validation. Le

premier mémorise l'événement, tandis que le deuxième, comme son nom l'indique,

valide ou non la prise en compte de l'événement.

Un bit

appelé GIE (Global Inerrupt Enable) du registre INTCON autorise ou inhibe

toutes les interruptions.

DEROULEMENT

D'UNE INTERRUPTION

Lorsqu'un

événement apparaît, le drapeau associé le mémorise en passant à l'état haut. Si

le bit de validation approprié est à "1", il y a alors une interruption

(on suppose que le bit GIE est à "1"). L'adresse contenue dans le PC

(Program Counter) est d'abord chargée dans le STACK, puis remplacée par la

valeur 0004H (adresse de la routine d'interruption). Le bit GIE passe à

"0" pour inhiber toutes les interruptions qui seraient simultanément

présentes. A la fin de la routine (instruction RETFIE), le bit GIE passe à

l'état haut (autorisant ainsi un autre événement) et le contenu du PC est

chargé avec la valeur du STACK.

![]() deux remarques importantes

sont à faire :

deux remarques importantes

sont à faire :

Le drapeau

reste à l’état haut même après le traitement de l’interruption. Par conséquent,

il faut toujours le remettre à "0" dans la routine.

Seul le PC est

sauvegardé. Si cela est nécessaire, les registres W et STATUS doivent alors

être sauvegardés en RAM puis restaurés à la fin de la routine pour que le

microcontroler puisse reprendre normalement le cours du programme.

LES

DIFFERENTES SOURCES D'INTERRUPTION

RBO DU

PORTB

Cette

interruption appelée INT est gérée par les bits INTF et INTE qui sont

respectivement le drapeau et le bit de validation.

Un bit

supplémentaire appelé INTEDG du registre d'option détermine le front, montant

(INTEDG=1) ou descendant (INTEDG=0), sur lequel sera déclenchée l'interruption.

RB4 A

RB7 DU PORTB

Lorsque ces

4 broches (ou l'une d'elle) sont configurées en ENTREE, elles entraînent une

interruption quand elles changent d'état. Les bits associés sont RBIF (drapeau)

et RBIE (bit de validation).

TMR0

Quand le

registre TMR0 passe de FFH à 00H (dépassement), le drapeau TOIF s'active.

L’interruption est validée par le bit TOIE.

EEPROM

Après chaque

cycle correct d'écriture, le drapeau EEIF (dans le registre EECON1) passe à

"1". Le bit de validation EEIE se trouve dans le registre INTCON.

![]() LA CONFIGURATION DE

L’OSCILLATTEUR.

LA CONFIGURATION DE

L’OSCILLATTEUR.

L'oscillateur

définit la vitesse d'exécution des instructions. Pour des raisons de

synchronisation, la fréquence interne de travail est celle de l’oscillateur

externe divisé par 4. Par exemple, avec un quartz de 4 MHz, le cycle

d'instruction sera d'une microseconde.

Le PIC16F84

peut fonctionner dans 4 configurations d’oscillateurs différents :

- LP (Low Power) : Avec une fréquence max de 200 KHz, il permet de réduire la

consommation du microcontroler.

- XT: C'est le mode d'utilisation le plus utilisé. Sa fréquence de travail peut

aller jusqu'à 4 MHZ max.

- HS (High Speed): C'est un mode de configuration pour l'utilisation de

fréquence très haute ( jusqu'à 10 MHZ).

-RC: Dans ce mode, c'est un réseau Résistance/Condensateur qui réalise l’oscillateur.

![]() Il est tout à fait

possible d'utiliser un oscillateur externe. Dans ce cas, la liaison se fait sur

l'entrée CKIN.

Il est tout à fait

possible d'utiliser un oscillateur externe. Dans ce cas, la liaison se fait sur

l'entrée CKIN.

Le mode de fonctionnement de l'oscillateur se configure lors de la

programmation du monochip dans le "mot de configuration".

EXEMPLE

D'APPLICATION EN MODE LP,XT ET HS.

Généralement,

les valeurs de C1 et C2 sont comprises entre 20 et 30pF.

EXEMPLE

D'APPLICATION EN MODE RC.

La fréquence

de l'oscillateur dépend essentiellement des conditions d'utilisation (tension

d'alimentation, température de fonctionnement, etc...) du microcontroler.

La fréquence d'horloge interne est disponible sur CKOUT (ceci est

uniquement valable pour le mode RC).

Une valeur

de la résistance comprise entre 3K et 100K est recommandée. En effet, une

valeur trop petite amortirait le signal (arrêt de l’oscillateur). A l'inverse,

une valeur trop grande rendrait l’oscillateur trop sensible aux bruits

(instabilité de la fréquence).

Cext n'a pas

de restriction. Cependant, une valeur comprise entre 20pF et 300 pF est

admise.

Il est

intéressant de noter qu’il est possible d'utiliser le mode RC sans Condensateur

externe. En effet, l'entrée CKIN a une capacité interne de 4 pF typique.

![]() LE RESET

LE RESET

Le RESET est

une interruption particulière qui initialise le microcontroler. Le PC (Program Counter)

est dans ce cas chargé avec l'adresse 0000H (début du programme).

Un RESET est

généré d'une manière soit matérielle, soit logicielle.

Comme le

montre le schéma, il existe cinq sources qui générent un RESET a savoir:

Le MCLR

(Master CLeaR) assure un RESET général du microcontroler quel que soit le mode

de fonctionnement du PIC16F84 (normal ou SLEEP). Actif à l'état bas et

prioritaire, il est le seul qui peut être provoqué de l'extérieur (broche 4).

le WDT est

un cas particulier. En mode normal, il génère un RESET ; en mode SLEEP, il

réveille le microcontroler (le programme continue à l'instruction suivante). 2

bits particuliers TO et PD du registre de STATUS indiquent la source du

déclenchement et permettent donc de réagir en fonction.

Le POR

(Power On Reset) qui n'est actif uniquement lors de la mise sous tension du

microcontroler. Il évite ainsi le rajout de composant externe (réseau RC) et

assure une bonne initialisation.

L' OST (

Oscillator Start-up Timer) s'assure que l'oscillateur du microcontroler est

stable.

Le PWRT

(PoWeR up Timer) est composé d'un oscillateur interne RC et d'un compteur. Il

maintient un RESET pendant 72 ms environ ( la durée dépend essentiellement de

la tension et de la température de fonctionnement).

CHRONOLOGIE

D'UN RESET.

Plusieurs

modules sont associés ensemble et permettent donc de réaliser une RAZ de bonne

qualité avec peu de composants externes.

Voici un

chronogramme d'un RESET classique:

DC copyright 2000

LE MODE SLEEP

![]() CONSIDERATIONS

CONSIDERATIONS

Certaines applications

(télécommande, clavier, ect...) fonctionnent avec une alimentation à pile pour

être transportable. Dans ce cas, outre la programmation, le choix d'un

microcontroler se fera sur sa consommation.

A noter que

celle-ci dépend essentiellement de l'alimentation et de la fréquence de

travail. Par exemple, avec une tension de 5V et une fréquence de 10 MHz, le

microcontroler absorbe un courant moyen de 10mA.

Pour faire

face à ce problème d'énergie, le PIC16F84 possède un mode de fonctionnement

particulier : le mode SLEEP. Dans ce mode, le courant peut chuter jusqu'à 26

microAmpere.

![]() LE MODE SLEEP

LE MODE SLEEP

En exécutant

l'instruction SLEEP, le microcontroler passe à un état statique. En fait,

l'oscillateur externe est arrêté. Le PC contient l'adresse de l'instruction

suivante. Le WDT est mis à "0" (s'il est validé). Le bit PD passe à

l'état bas et TO à l'état haut. Enfin, les PORTS conservent l’état dans lequel

ils étaient avant l'instruction SLEEP.

![]() Pour diminuer davantage la

consommation, les E/S des ports doivent être reliées à l'alimentation (VDD ou

VSS) et/ou aucun circuit extérieur ne doit drainer le courant provenant

de ces derniers.

Pour diminuer davantage la

consommation, les E/S des ports doivent être reliées à l'alimentation (VDD ou

VSS) et/ou aucun circuit extérieur ne doit drainer le courant provenant

de ces derniers.

![]() LE "REVEIL" DU

MICROCONTROLER

LE "REVEIL" DU

MICROCONTROLER

Le

"réveil" consiste tout simplement à démarrer l'oscillateur. Une fois

le régime établi, le programme continue.

Lorsqu'il

est dans le mode SLEEP, seules 5 sources peuvent relancer le PIC16C84 (MCLR,

WDT, Interruption de fin de cycle d'écriture de l'EEPROM, l'Interruption RB0 et

l'Interruption de changement d'état RB4 à RB7).

Le MCLR

réalise un RESET général, ce qui permet au microcontroler de démarre à

l'adresse 0000H (début du programme).

Lorsque le

registre WDT est activé, il "réveille" le PIC16C84 quand le Time Out

(TO) est à "1" (dépassement du registre WDT). Le microcontroler

poursuit alors le programme.

Si les

interruptions sont validées, le programme exécute alors l'instruction qui suit

l'instruction SLEEP. Ensuite, suivant l'état du GIE, le microcontroler continue

le programme (GIE=0), ou traite la routine d'interruption (GIE=1).

REMARQUE: Si

une interruption intervient avant l'instruction SLEEP, celle-ci est alors

exécutée comme une opération NOP (No Operation) et le WDT n'est pas effacé.

LE JEU D’INSTRUCTION

![]() LE

LANGAGE ASSEMBLEUR

LE

LANGAGE ASSEMBLEUR

Le langage

assembleur est une interface entre l’homme et le microcontroler pour la

compréhension d’un programme.

En effet, il

est difficile pour l’homme d’écrire ou de comprendre une représentation binaire

d’une suite d’instructions. Quant au microcontroler, il ne reconnaît qu’une

suite de 0 et de 1 (langage binaire).

Pour une

représentation plus explicite d’un langage binaire, on utilise le langage

assembleur où les instructions sont représentées par leur mnémonique

(abréviation anglaise d’une instruction) et les données binaires sont écrites

en hexadécimal (base 15), décimal (base 10), octal (base 8) ou encore binaire

(base 2).

Outre les

mnémoniques, le langage assembleur contient également des directives : ce

sont des instructions qui donnent à l’assembleur des consignes lors de la

compilation du programme, comme l’origine du programme, la réservation de

données, etc…

L’assembleur

convertit alors ces instructions en code binaire assimilable par le monochip.

Enfin, on

peut noter au passage qu‘il existe des assembleurs s‘exécutant sur différentes

plate-formes (DOS, WINDOWS) avec une multitude de langages de programmation

(programmation en BASIC, en C, en langage mnémonique, ect…).

![]() LE FICHIER SOURCE, LIST,

OBJET ET HEXADECIMAL

LE FICHIER SOURCE, LIST,

OBJET ET HEXADECIMAL

Un fichier

source contient le programme écrit dans un langage compréhensible pour l’homme.

Edité sous le format ASCII, il décrit sous une forme le plus souvent mnémonique

les instructions que doit exécuter le microcontroler. Un simple traitement de texte

suffit donc pour élaborer le programme (avec notepad par exemple).

Le fichier

source est divisé en 3 colonnes principales :

![]() Dans la

colonne de gauche sont inscrites les étiquettes (ou label) qui permettent de

nommer une variable ou de définir un emplacement dans la mémoire programme

(utilisé notamment pour les sous-programmes et les boucles).

Dans la

colonne de gauche sont inscrites les étiquettes (ou label) qui permettent de

nommer une variable ou de définir un emplacement dans la mémoire programme

(utilisé notamment pour les sous-programmes et les boucles).

![]() La colonne

du milieu décrit l’instruction (ou mnémonique) que devra exécuter le

microcontroler.

La colonne

du milieu décrit l’instruction (ou mnémonique) que devra exécuter le

microcontroler.

![]() Enfin, la

colonne de droite permet au développer d’écrire des commentaires susceptibles

de rendre le programme plus lisible.

Enfin, la

colonne de droite permet au développer d’écrire des commentaires susceptibles

de rendre le programme plus lisible.

Généralement

l’extension du fichier est *.ASM.

L’assembleur

traduit le fichier source en différents fichiers au choix du concepteur :

Fichier

LIST : l’assembleur transcrit le fichier source en un fichier comportant

le code machine à gauche et le fichier source à droite. Ce type de fichier est

utilisé notamment pour la simulation logiciel.

L’extension

d’un fichier LIST est *.LST.

Fichier

objet : l’assembleur convertit un fichier source en un fichier OBJET.

Chaque fichier OBJET est une portion de programme et peut être lié aux autres.

L’assembleur compile alors les fichiers OBJET pour former le programme.

L’extension

est *.OBJ.

Fichier

HEXDECIMAL : Le fichier hexadécimal est le seul fichier adapté au

microcontroler. Il contient le code machine et permet de programmer le monochip

avec l’outil de programmation adéquat.

L’extension

par défaut est *.HEX.

![]() LE JEU D’INSTRUCTION DU

PIC16F84

LE JEU D’INSTRUCTION DU

PIC16F84

Un

microcontroler est caractérisé non seulement par sa structure matérielle mais

aussi par son jeu d’instructions qui permet de traiter les données.

Le PIC16F84

a un jeu d’instructions relativement limité mais possède une architecture

interne (RISC) qui permet une programmation efficace et rapide (toutes les

instructions, exceptées les sauts, s'exécute en un cycle d'horloge).

De plus, le

monochip utilise 3 modes d’adressage différents (manière d’accéder à une

donnée) : direct, indirect et relatif pour les instructions de

branchement.

Les bits du

status affectés sont indiqués sur un fond rouge.

|

instructions liées aux

variables |

ADDLW |

ANDLW |

IORLW |

MOVLW |

RETLW |

SUBLW |

XORLW |

|

|

instructions liées aux

données |

ADDWF |

ANDWF |

CLRF |

COMF |

DECF |

DECFSZ |

INCF |

INCFSZ |

|

|

IORWF |

MOVF |

MOVWF |

NOP |

RLF |

RRF |

SUBWF |

XORWF |

|

instructions liées aux

bits |

BCF |

BSF |

BTFSC |

BTFSS |

|

|

|

|

|

autres instructions |

SWAPF |

CALL |

GOTO |

RETFIE |

RETURN |

CLRWDT |

SLEEP |

|

LES

INSTRUCTIONS OPERANT AVEC LES VARIABLES

![]() MNEMONIQUE

MNEMONIQUE

ADDLW

SYNTAX

ADDLW

K ; K compris entre 0 et 255

DESCRIPTION

Additionne

le contenu du registre W avec la valeur K. le résultat se trouve dans le

registre W.

EXEMPLE

ADDLW

0X30 ; ajoute au registre W la valeur hexadécimale 30

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

ANDLW

SYNTAX

ANDLW

K ; K compris entre 0 et 255

DESCRIPTION

Réalise un

ET logique entre la valeur du registre W et la valeur littéral K. le résultat

se trouve dans le registre W.

EXEMPLE

ANDLW

0X30 ; ET logique entre la valeur du registre W et 0X30.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

IORLW

SYNTAX

IORLW

K ; K compris entre 0 et 255

DESCRIPTION

Réalise un

OU logique entre la valeur du registre W et la valeur littéral. Le résultat se

trouve dans le registre W.

EXEMPLE

IORLW

0X30 ; OU logique entre le registre W et 0X30.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

MOVLW

SYNTAX

MOVLW

K ; K compris entre 0 et 255.

DESCRIPTION

Charge le

registre W avec la valeur littéral K.

EXEMPLE

MOVLW

0X30 ; la valeur du registre W est maintenant égale à

30

![]() MNEMONIQUE

MNEMONIQUE

RETLW

SYNTAX

RETLW

K ; K compris entre 0 et 255.

DESCRIPTION

Instruction

utilisée lors d’un retour d’un sous-programme. Le registre W est chargé avec la

valeur littérale K et le PC avec la valeur de l’adresse de retour (STACK).

EXEMPLE

CALL

LAS-BAS ; appelle le sous programme LAS-BAS.

.

.

; autres instructions.

.

.

LAS-BAS

RETLW 0X30 ; le registre W est chargé avec la valeur 30 et retour au

; programme principal.

![]() MNEMONIQUE

MNEMONIQUE

SUBLW

SYNTAX

SUBLW

K ; K compris entre 0 et 255.

DESCRIPTION

Soustrait la

valeur littérale K au registre W. le résultat se trouve dans le registre W.

EXEMPLE

SUBLW

0X30 ; soustrait la valeur 30 au registre W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

XORLW

SYNTAX

XORLW

K ; K compris entre 0 et 255.

DESCRIPTION

Effectue un

OU EXCLUSIF entre le registre W et la valeur littéral K. le résultat se trouve

dans le registre W.

EXEMPLE

XORLW

0X30 ; OU EXCLUSIF entre le registre W et la valeur 30.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

D |

LES

INSTRUCTIONS OPERANT SUR LES DONNEES

![]() MNEMONIQUE

MNEMONIQUE

ADDWF

SYNTAX

ADDWF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Additionne

le contenu du registre W avec la valeur contenue dans le registre fichier F. si

DIR=0, alors le résultat sera dans le registre W. si DIR=1, le résultat est

stocké dans le registre F.

EXEMPLE

MOVLW

0X30 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

ADDWF

VAL ,0 ; additionne le registre W et F. le résultat (0X60) est stocké dans

W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

ANDWF

SYNTAX

ANDWF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Réalise un

ET logique entre le contenu du registre W et la valeur contenue dans le

registre fichier F. si DIR=0, alors le résultat sera dans le registre W. si

DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

MOVLW

0X30 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

ANDWF

VAL ,0 ; effectue un Et entre le registre W et F. le résultat est stocké

dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

CLRF

SYNTAX

CLRF

F ; F compris entre 0 et 127.

DESCRIPTION

Le contenu

du registre F est effacé.

EXEMPLE

CLRF

VAL ; efface le contenu de VAL

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

COMF

SYNTAX

COMF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Effectue le

complément a 2 du registre fichier F. si DIR=0, le résultat sera alors dans le

registre W. si DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

COMF

VAL ,0 ; complément à 2 de VAL. le résultat est

stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

DECF

SYNTAX

DECF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

la valeur

contenue dans le registre fichier F est décrémenté de 1. si DIR=0, le résultat

sera alors dans le registre W. si DIR=1, le résultat est stocké dans le

registre F.

EXEMPLE

DECF

VAL ,0 ; décrémente le registre VAL. le résultat

est stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

DECFSZ

SYNTAX

DECFSZ

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

la valeur

contenue dans le registre fichier F est décrémentée de 1. si DIR=0, alors le

résultat sera dans le registre W. si DIR=1, le résultat est stocké dans le

registre F. si le résultat est nul, alors l’instruction suivante est sautée.

EXEMPLE

MOVLW

0X1 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

DECFSZ

VAL ,0 ; décrémente F. le résultat est stocké dans W. comme le résultat

est nul alors

ICI NOP

NOICI NOP ;

le programme saute à l’adresse NOICI.

![]() MNEMONIQUE

MNEMONIQUE

INCF

SYNTAX

INCF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

la valeur

contenue dans le registre fichier F est incrémentée de 1. si DIR=0, le résultat

sera alors dans le registre W. si DIR=1, le résultat est stocké dans le

registre F.

EXEMPLE

INCF

VAL ,0 ; incrémente le registre F. le résultat est stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

INCFSZ

SYNTAX

INCFSZ

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

la valeur

contenue dans le registre fichier F est incrémentée de 1. si DIR=0, alors le

résultat sera dans le registre W. si DIR=1, le résultat est stocké dans le

registre F. si le résultat est nul, l’instruction suivante est alors sautée.

EXEMPLE

MOVLW

0XFF ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

INCFSZ

VAL ,0 ; décrémente F. le résultat est stocké dans W.

comme le résultat est nul alors

ICI

NOP

NOICI

NOP ; le programme saute à

l’adresse NOICI.

![]() MNEMONIQUE

MNEMONIQUE

IORWF

SYNTAX

IORWF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

REALISE UN

OU logique entre le contenu du registre W et la valeur contenue dans le

registre fichier F. si DIR=0, le résultat sera alors dans le registre W. si

DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

MOVLW

0X30 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

IORWF

VAL ,0 ; OU logique entre le registre W et F. le

résultat est stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

MOVF

SYNTAX

MOVF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

le contenu

du registre F est déplacé dans le registre de destination. si DIR=0, il sera

alors dans le registre W. si DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

MOVLW

0X30 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

MOVF

VAL ,0 ; déplace le registre F vers W. le résultat

est stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

MOVWF

SYNTAX

MOVWF

F ; F compris entre 0 et 127.

DESCRIPTION

Déplace le

contenu du registre W dans le registre fichier F.

EXEMPLE

MOVLW

0X30 ; stocke la valeur 30 dans W

MOVWF

VAL ; stocke la valeur dans VAL

![]() MNEMONIQUE

MNEMONIQUE

NOP

SYNTAX

NOP

DESCRIPTION

Effectue

aucune opération ( NO Operation). Utilisé dans des boucles de temporisation.

EXEMPLE

NOP

![]() MNEMONIQUE

MNEMONIQUE

RLF

SYNTAX

RLF

F,DIR ; F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Le contenu

dans le registre fichier F est décalé de 1 bit vers la gauche. Le bit qui

s’intercale est le reflet du drapeau de retenue. si DIR=0, le résultat sera

alors dans le registre W. si DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

MOVLW 00 ;

stocke la valeur 00 dans W

MOVWF VAL ;

stocke la valeur dans VAL

RLF VAL,0 ;

effectue une rotation du registre F. le résultat est stocké dans W. si le

drapeau de retenue est à 1, alors on aura dans W la valeur 01.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

RRF

SYNTAX

RRF

F,DIR ;F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Le contenu

dans le registre fichier F est décalé de 1 bit vers la droite. Le bit qui

s’intercale est le reflet du drapeau de retenue. si DIR=0, le résultat sera

alors dans le registre W. si DIR=1, le résultat est stocké dans le registre F.

EXEMPLE

MOVLW

00 ; stocke la valeur 00 dans W

MOVWF

VAL ; stocke la valeur dans VAL

RLF

VAL,0 ; effectue une rotation du registre F. le

résultat est stocké dans W. si le drapeau de retenue est à 1, on aura alors

dans W la valeur 01.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

SUBWF

SYNTAX

SUBWF

F,DIR ;F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

si DIR=0, le

résultat sera alors dans le registre W. si DIR=1, le résultat est stocké dans le

registre F.

EXEMPLE

MOVLW

00 ; stocke la valeur 00 dans W

MOVWF

VAL ; stocke la valeur dans VAL

SUBWF

VAL,0 ; effectue une soustraction entre W et F. le

résultat est stocké dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

![]() MNEMONIQUE

MNEMONIQUE

XORWF

SYNTAX

XORWF

F,DIR ;F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Effectue un

OU exclusif entre le registre W et le registre F. Si DIR=0, le résultat

sera alors dans le registre W. si DIR=1, le résultat est stocké dans le

registre F.

EXEMPLE

MOVLW

00 ; stocke la valeur 00 dans W

MOVWF

VAL ; stocke la valeur dans VAL

XORWF

VAL,0 ; Réalise un OU exclusif. Le résultat est stocké

dans W.

LES BITS

DU STATUS AFFECTES

|

C |

Z |

DC |

LES INSTRUCTIONS OPERANT

SUR LES BITS

![]() MNEMONIQUE

MNEMONIQUE

BCF

SYNTAX

BCF

F,DIR ;F compris entre 0 et 127. DIR compris entre 0 et

7.

DESCRIPTION

Met à zéro

le bit DIR du registre F.

EXEMPLE

BCF

VAL,3 ; Le bit 3 du registre F est à zéro.

![]() MNEMONIQUE

MNEMONIQUE

BSF

SYNTAX

BSF

F,DIR ;F compris entre 0 et 127. DIR compris entre 0 et

7.

DESCRIPTION

Met à

"1" le bit DIR du registre F.

EXEMPLE

BSF

VAL,3 ; Le bit 3 du registre F est à

"1".

![]() MNEMONIQUE

MNEMONIQUE

BTFSC

SYNTAX

BTFSC

F,DIR ;F compris entre 0 et 127. DIR compris entre 0 et

7.

DESCRIPTION

Si le bit

DIR du registre F est à zéro, alors la prochaine instruction est

"sautée".

EXEMPLE

BTFSC

VAL,3 ; Test le bit 3 du registre F.

ICI

NOP ; Si le bit est à "0"

alors cette instruction ne sera pas executée et passera directement à LA.

LA

NOP ;

![]() MNEMONIQUE

MNEMONIQUE

BTFSS

SYNTAX

BTFSS

F,DIR ;F compris entre 0 et 127. DIR compris entre 0 et

7.

DESCRIPTION

Si le bit

DIR du registre F est à "1", alors la prochaine instruction est

"sautée".

EXEMPLE

BTFSS

VAL,3 ; Test le bit 3 du registre F.

ICI

NOP ; Si le bit est à "1"

alors cette instruction ne sera pas executée et passera directement à LA.

LA

NOP ;

LES AUTRES INSTRUCTIONS

![]() MNEMONIQUE

MNEMONIQUE

SWAPF

SYNTAX

SWAPF

F,DIR ;F compris entre 0 et 127. DIR=0 ou 1.

DESCRIPTION

Effectue une

inversion des deux quartets du registre F. Si DIR=0 alors le résultat sera dans

le registre W. Si DIR=1, le résultat est stocké dans F

EXEMPLE

MOVLW

0X0F

MOVWF

VAL ; VAL=0F

SWAPF

VAL,1 ;VAL=F0

![]() MNEMONIQUE

MNEMONIQUE

CALL

SYNTAX

CALL

K ; K est un label.

DESCRIPTION

Appelle le

sous- programme k. Le PC est chargé avec l'adresse du label. L'adresse de

retour (PC+1) est stockée dans le STACK.

![]() MNEMONIQUE

MNEMONIQUE

GOTO

SYNTAX

GOTO

K ; K est un label.

DESCRIPTION

Le programme

saute à l'adresse K.

![]() MNEMONIQUE

MNEMONIQUE

RETFIE

SYNTAX

RETFIE

DESCRIPTION

Fin d'une

routine d'interruption. le PC est charge avec l'adresse contenue dans le STACK

![]() MNEMONIQUE

MNEMONIQUE

RETURN

SYNTAX

RETURN

DESCRIPTION

Fin d'un

sous- programme. Le PC est chagé avec l'adresse contenue dans le STACK.

![]() MNEMONIQUE

MNEMONIQUE

CLRWDT

SYNTAX

CLRWDT

DESCRIPTION

Efface le

WDT et le prescaler. Les bits TO et PD sont mis à "1".

![]() MNEMONIQUE

MNEMONIQUE

SLEEP

SYNTAX

SLEEP

DESCRIPTION

Le

microcontroler est en mode SLEPP. l'oscillateur est arrêté. le bit TO est à

"1". Le bit PD est à "0". Le WDT et le prescaler sont

effacés.

L'ADRESSAGE INDIRECTE

L'

UTILISATION

L'adressage

indirecte permet d'acceder à plusieurs données sans spécifier leur adresse

effective. L'interet est de permettre l'acces à des variables consecutives avec

un minimum d'instructions.

LE PRINCIPE

On utilise

les deux registres INDF et FSR du PIC. L'un contient l'adresse (FSR) et l'autre

la valeur de la variable (INDF). Lire ou écrire dans INDF revient à lire ou

écrire dans la variable.

EXEMPLE

INITIALISATION DE PLUSIEURS VARIABLES

Dans cet

exemple, il faut initialiser 20 variables avec la valeur CD (hex).

; Déclaration des variables ORG H'0C'VAR RES 20 ;Les 20 variablesCOMPT RES 1 ;une variable de comptage ;programme principal ORG 0 GOTO DEBUT ; vecteur interruption ORG 4 REFIE ;Le programme DEBUT MOVLW 0X0C ;W=0C début de la RAM. MOVWF FSR ;FSR=0C Adresse de la RAM dans le FSR. MOVLW .20 MOVWF COMPT ;La variable COMPT contient 20. MOVLW 0XCD ;La variable a écrire dans la RAM.LOOP MOVWF INDF ;On écrit 0C à l'adresse de FSR. INCF FSR ;Maintenant, FSR pointe l'adresse suivante. DECFSZ COMPT,F ; et on le fait 20 fois. GOTO LOOP END

MEMORISER DES OCTETS RECUES

un exemple

qui montre comment mémoriser des octets provenant d'une transmission série.

; Déclaration des variables ORG H'0C'VARRX RES 8 ;Les 8 variablesCOMPT RES 1 ;une variable de comptage ;programme principal ORG 0 GOTO DEBUT ; vecteur interruption ORG 4 REFIE ;Le programme DEBUT MOVLW 0X0C MOVWF FSR ;FSR=0C Adresse de la RAM dans le FSR.MOVLW 0X08

MOVWF COMPT LOOP CALL RX ;Ce sous-programme renvoie dans W l'octet recue MOVWF INDF ;On l'écrit à l'adresse de FSR. INCF FSR ;Maintenant, FSR pointe l'adresse suivante. DECFSZ COMPT,F ; et on le fait 8 fois. GOTO LOOP END

LE TIMER/COMPTEUR

L'

UTILISATION

Le module

TIMER/COMPTEUR permet soit de réaliser une base de temps de précision, soit de

compter les implusions provenant de l'entrée RA0.

On peut

associer au module le prescaler (diviseur).

LE PRINCIPE

La

programmation de ce module TIMER/COMPTEUR est assez simple. Par contre sa

gestion peut etre délicate :

- soit on

lit le registre TMR0 : dans ce cas une lecture périodique du registre est

obligatoire.

- soit on

passe par le jeu des interruptions: On attend que le registre TMR0 génere une

interruption pour effectuer le traitement.

EXEMPLE

UNE BASE DE TEMPS SIMPLE.

Dans cet

exemple, une led cablée sur RB0 clignotte à une fréquence de 1s ( 500ms éteint

et 500 ms allumée)

;programme principal ORG 0 GOTO DEBUT ; vecteur interruption ORG 4 REFIE ;Le programme DEBUT MOVLW 0X05 MOVWF EEADR ;Adresse de la donnée dans l'EEPROM.

BSF STATUS,RP0 ;On passe en page1. BSF EECON1,RD ;Validation de la lecture. BCF STATUS,RP0 ;On passe en page0. MOVF EEDATA,0 ;La donnée se trouve dans W END

UN COMPTEUR SIMPLE.

Un petit

exemple qui montre comment incrémenter une variable de 1 a chaque fois que le

compteur recoit 100 implusions.

;programme principal ORG 0 GOTO DEBUT ; vecteur interruption ORG 4 REFIE ;Le programme DEBUT MOVLW 0X02 MOVWF EEADR ;Adresse de la donnée dans l'EEPROM.

MOVLW 0XDC MOVWF EEDATA ;Valeur de la donnée a écrire. BSF STATUS,RP0 ;On passe en page1. BCF INTCON,GIE ;On inhibe les interruptions. BSF EECON1,WREN ;Validation de l'écriture. MOVLW 0X55 ;Cette séquence est obligatoire

MOVWF EECON2

MOVLW 0XAA MOVWF EECON2 BSF EECON1,WR LOOP BTFSS EECON1,EEIF ;On attend la fin de cycle d'écriture GOTO LOOP BCF EECON1,EEIF ;On efface le drapeau BSF INTCON,GIE ;On valide les interruptions ;(dans le cas ou elles sont utilisées dans le programme) BCF STATUS,RP0 ;On passe en page0.END

DC copyright 1999

LA TEMPORISATION

L'

UTILISATION

Une

temporisation permet de synchroniser le microcontrôleur avec des événements

généralement extérieurs.

LE PRINCIPE

Le principe

est d' exécute un nombre de fois une boucle de durée X. Ensuite, on

"ajuste" le temps avec des instructions ( NOP par exemple).

EXEMPLE

UNE TEMPORISATION DE 10µS

On utilise

un sous-programme appelé TEMPO d'une durée de 10 µS. Lorsqu'on appelle cette

routine tient, on tient compte de l'instruction CALL ( qui se réalise en deux

cycles d'instructions).

; Le pic est cadencé avec un quartz de 4MHz ; ce qui correspond à un cycle d'instruction de 1 µS. TEMPO NOP ;T=3µS NOP ;T=4µS NOP NOP NOP NOP ;T=8µS

RETURN ;T=10µS ;programme principal CALL TEMPO ;Le pic attend 10µS

UNE TEMPORISATION DE 10 µS (autre exemple)

Même

principe mais on utilise l'instruction GOTO ( pour gagner quelques

instructions)

; Le pic est cadencé avec un quartz de 4MHz; ce qui correspond à un cycle d'instruction de 1 µS. TEMPO GOTO LOOP1 ;T=4µSLOOP1 GOTO LOOP2 ;T=6µSLOOP2 GOTO LOOP3LOOP3 RETURN ; T=10µS ;programme principal CALL TEMPO ;Le pic attend 10µS

UNE TEMPORISATION DE 100µS

On utilise

un sous-programme appelé TEMPO d'une durée de 100 µS. Lorsqu'on appelle cette

routine tient, on tient compte de l'instruction CALL ( qui se réalise en deux

cycles d'instructions).

; Le pic est cadencé avec un quartz de 4MHz; ce qui correspond à un cycle d'instruction de 1 µS. TEMPO MOVLW 0X18 ;W=24 (en décimal). durée=1µSLOOP ADDLW 0XFF ;W=W-1. durée=1µS BTFSS STATUS,Z ;on teste si le resultat est nul. durée=1µS Si Z=0 sinon ;durée=2µS GOTO LOOP ; retourne en LOOP W>0. durée=1µS RETURN ;T=100µS. durée=2µS ;T=7+22*4+5 ;programme principal CALL TEMPO ;Le pic attend 100µS

UNE TEMPORISATION DE 1mS

On utilise

un sous-programme appelé TEMPO d'une durée de 1mS. Lorsqu'on appelle cette

routine, on tient compte de l'instruction CALL ( qui se réalise en deux cycles

d'instructions).

; Le pic est cadencé avec un quartz de 4MHz; ce qui correspond à un cycle d'instruction de 1 µS. TEMPO MOVLW 0XF9 ;W=249 (en décimal). durée=1µSLOOP ADDLW 0XFF ;W=W-1. durée=1µS BTFSS STATUS,Z ;on teste si le résultat est nul. durée=1µS Si Z=0 sinon ;durée=2µS GOTO LOOP ; retourne en LOOP W>0. durée=1µS RETURN ;T=1mS. durée=2µS ;T=7+247*4+5 ;programme principal CALL TEMPO ;Le pic attend 1mS

UNE TEMPORISATION DE 10mS

Jusqu'a

présent, les temporisations etaient assez courte et pouvaient être exécuter

avec une seule boucle. Pour des durée plus grande, deux solutions se

présentent:

- soit on diminue la fréquence de

travail du PIC (déconseillé) et on réalise les tempos avec une seule

boucle.

- soit on conserve la cadence et

dans ce cas, on imbrique des boucles.

Il est

évident ,pour des raisons de commodités, que la deuxième méthode est la plus

réaliste.

; Le pic est cadencé avec un quartz de 4MHz; ce qui correspond à un cycle d'instruction de 1 µS. TEMPO MOVLW 0X0A ;W=10 (en décimal). MOVWF TEMP_VAR ;W dans la variable TEMP_VAR.LOOP1 MOVLW 0XF9 ;W=249LOOP ADDLW 0XFF ;W=W-1. BTFSS STATUS,Z ;teste si Z=0 GOTO LOOP DECFSZ TEMP_VAR,F ;décrémente TEM_VAR. Si TEM_VAR=0 alors saute la prochaine instruction

GOTO LOOP1 ;sinon retourne en LOOP1. NOP ;on ajuste la duréeNOP

NOP NOP NOPRETURN

;programme principal CALL TEMPO ;Le pic attend 10mS

UNE TEMPORISATION DE 100mS

Elle est

réalisée sur le principe des boucles imbriquées.Lorsqu'on appelle cette

routine, on tient compte de l'instruction CALL ( qui se réalise en deux cycles

d'instructions).